CryptoDB

Improved Leakage-Resistant Authenticated Encryption based on Hardware AES Coprocessors

| Authors: |

|

|---|---|

| Download: | |

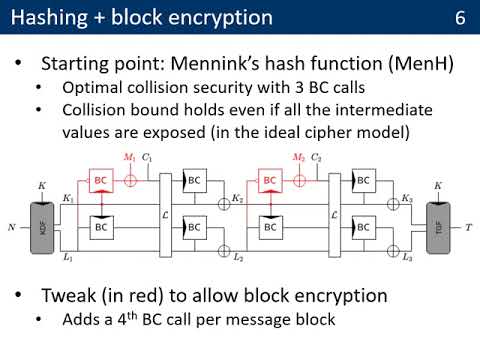

| Abstract: | We revisit Unterstein et al.’s leakage-resilient authenticated encryption scheme from CHES 2020. Its main goal is to enable secure software updates by leveraging unprotected (e.g., AES, SHA256) coprocessors available on low-end microcontrollers. We show that the design of this scheme ignores an important attack vector that can significantly reduce its security claims, and that the evaluation of its leakage-resilient PRF is quite sensitive to minor variations of its measurements, which can easily lead to security overstatements. We then describe and analyze a new mode of operation for which we propose more conservative security parameters and show that it competes with the CHES 2020 one in terms of performances. As an additional bonus, our solution relies only on AES-128 coprocessors, an |

Video from TCHES 2021

BibTeX

@article{tches-2021-31297,

title={Improved Leakage-Resistant Authenticated Encryption based on Hardware AES Coprocessors},

journal={IACR Transactions on Cryptographic Hardware and Embedded Systems},

publisher={Ruhr-Universität Bochum},

volume={2021, Issue 3},

pages={641-676},

url={https://tches.iacr.org/index.php/TCHES/article/view/8988},

doi={10.46586/tches.v2021.i3.641-676},

author={Olivier Bronchain and Charles Momin and Thomas Peters and François-Xavier Standaert},

year=2021

}